IT之家 10 月 24 日消息,在芯片制造这项关乎现代科技命脉的精密工程中,光刻技术扮演着如同画笔般的核心角色,负责将复杂的电路图案一丝不苟地“绘制”在硅晶圆上。

然而,在这个核心流程中,一个关键的微观世界 ——“光刻胶在显影液中的行为”却如同一个无法窥探的“黑匣子”,长久以来困扰着业界,并成为提升 7nm 及更先进制程芯片良率的关键瓶颈。

近日,北京大学彭海琳教授团队合作通过冷冻电子断层扫描技术,首次在原位状态下解析了光刻胶分子在液相环境中的微观三维结构、界面分布与缠结行为,成功揭开了这个“黑匣子”的神秘面纱。

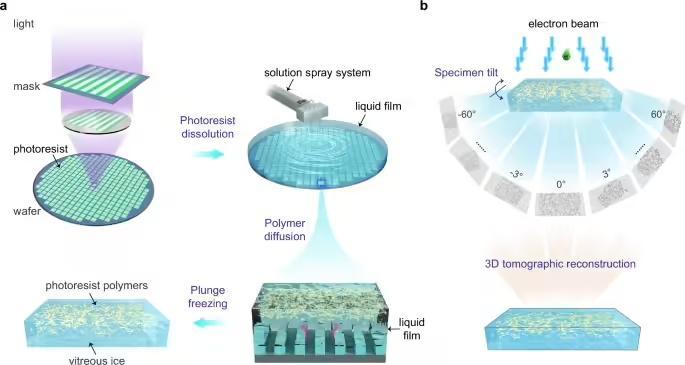

这项突破性研究由北京大学化学与分子工程学院彭海琳教授、高毅勤教授、郑黎明博士联合清华大学王宏伟教授、香港大学刘楠博士等共同完成。研究团队创造性地将原本主要用于生命科学研究的冷冻电子断层扫描(cryo-ET)技术,首次引入半导体制造领域。这项技术的精妙之处在于,它能以极快的速度(超过每秒一万摄氏度)将显影液连同其中的光刻胶分子瞬间冻结在它们的“工作状态”,如同按下时间的暂停键,完整保留了这些分子在液态环境中的真实构象。随后,利用先进的成像和三维重建技术,科学家们成功获得了分辨率优于 5 纳米的光刻胶微观三维“高清全景图”,首次在原位状态下清晰地揭示了光刻胶分子在显影液中的三维结构、界面分布以及相互缠绕(缠结)的行为细节。

这一前所未有的观测带来了颠覆性的新发现。与以往认为光刻胶溶解后会均匀分散在液体中的假设不同,三维图像清晰显示,绝大部分光刻胶分子倾向于聚集并吸附在液体和空气的界面上。更重要的是,研究首次在真实空间中直接观察到了光刻胶分子之间的“凝聚缠结”现象 —— 它们并非紧密交织,而是通过较弱的分子作用力松散地连接在一起,类似于局部平行排列的状态。正是这些吸附在界面上并发生缠结的分子,容易形成尺寸较大(平均约 30 纳米,部分甚至超过 40 纳米)的团聚颗粒。在芯片制造的显影环节中,这些团聚体极易重新沉积到极其精密的电路图案上,造成致命的缺陷。研究人员发现,一块 12 英寸晶圆上因此产生的缺陷数量可高达数千个,严重制约了先进芯片的量产良率。

深入理解现象背后的成因是解决问题的关键。团队通过计算机模拟(分子动力学模拟)验证了实验结果,并揭示了分子聚集和缠结的能量驱动机制及可逆特性。基于这些深刻洞察,研究团队提出了两项既简单又高效、且能与现有芯片生产线无缝兼容的创新解决方案:一是通过适当提高显影前的烘烤温度,利用缠结的热敏感性,有效促使大团聚体解离成更小、更分散的分子链;二是在显影过程中优化工艺,确保晶圆表面始终覆盖一层连续的液体薄膜,这层薄膜就像一张高效的“捕网”,能捕获并将吸附在界面上的分子团簇冲刷带走,阻止其回落污染电路图案。

令人振奋的是,当这两种策略结合应用后,12 英寸晶圆上由光刻胶残留引起的图案缺陷被成功消除了超过 99%。这一成果意味着,长期困扰先进芯片制造的显影缺陷问题,获得了具有高度可行性的优化路径。

该研究的意义远超光刻领域本身。其所展现的冷冻电子断层扫描技术威力,为在原子 / 分子尺度上原位研究各类发生在液体环境中的化学反应(如催化、合成乃至生命过程)提供了强大的通用工具。对于芯片产业而言,精准掌握液体中聚合物材料的微观行为,将极大地推动包括光刻、蚀刻、清洗等在内的多个先进制造关键环节的缺陷控制和良率提升,为制造性能更强、更可靠的下一代芯片铺平道路。

这项标志性成果已于 9 月 30 日发表在顶尖学术期刊《自然・通讯》上。IT之家附论文地址:https://www.nature.com/articles/s41467-025-63689-4